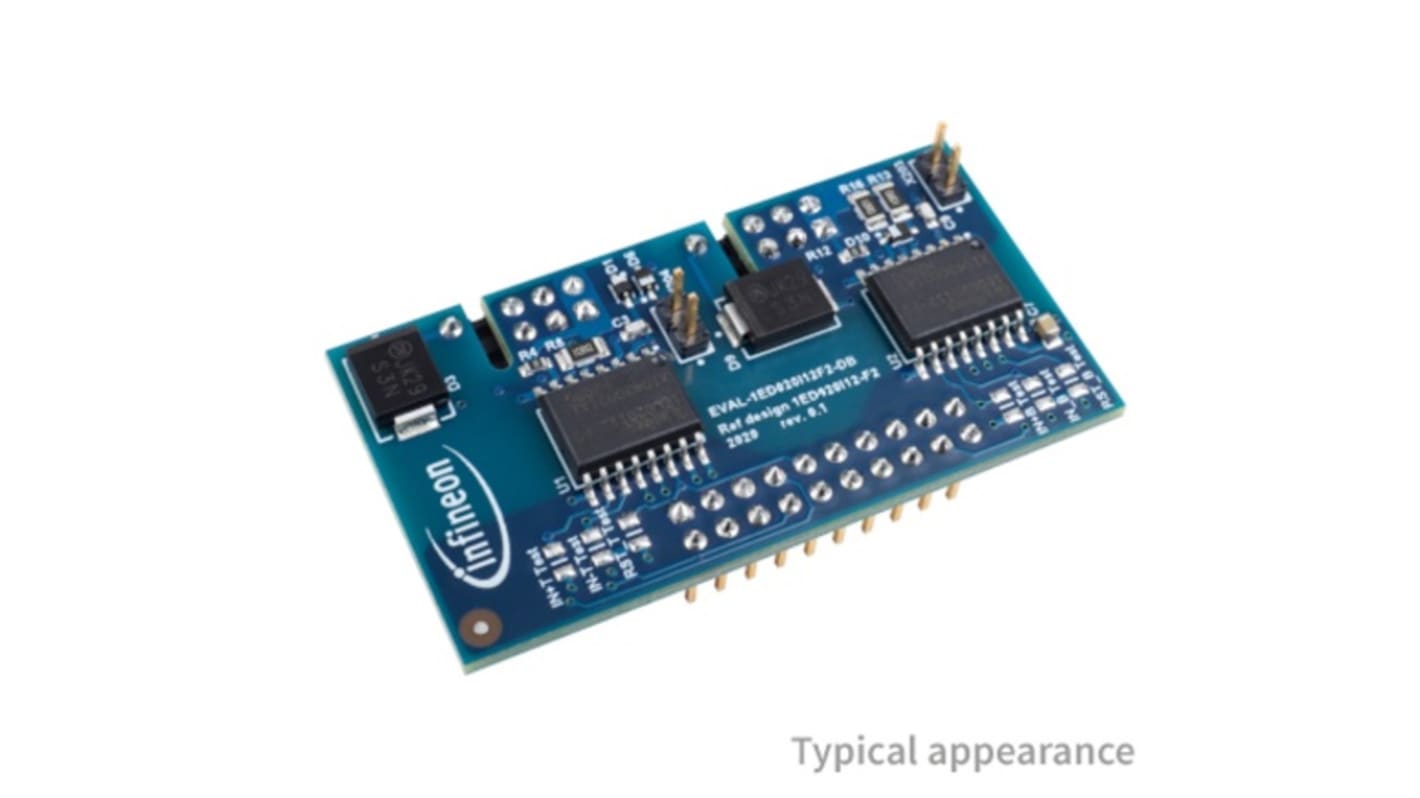

Infineon Enhanced isolated driver 1ED020I12-F2 Evaluierungsplatine, EVAL-1ED020I12F2-DB IGBT-Gate-Ansteuerung

- RS Best.-Nr.:

- 248-9724

- Herst. Teile-Nr.:

- EVAL1ED020I12F2DBTOBO1

- Marke:

- Infineon

Derzeit nicht erhältlich

Wir wissen nicht, ob wir diesen Artikel noch einmal auf Lager haben werden. RS beabsichtigt, ihn bald aus dem Sortiment zu nehmen.

- RS Best.-Nr.:

- 248-9724

- Herst. Teile-Nr.:

- EVAL1ED020I12F2DBTOBO1

- Marke:

- Infineon

Technische Daten

Mehr Infos und technische Dokumente

Rechtliche Anforderungen

Produktdetails

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | Infineon | |

| Funktion für Stromüberwachungseinheiten | IGBT-Gate-Ansteuerung | |

| Zum Einsatz mit | Doppelimpuls-Prüfplatinen | |

| Kit-Klassifizierung | Tochterplatine | |

| Vorgestelltes Gerät | Enhanced isolated driver 1ED020I12-F2 | |

| Kit-Name | EVAL-1ED020I12F2-DB | |

| Alle auswählen | ||

|---|---|---|

Marke Infineon | ||

Funktion für Stromüberwachungseinheiten IGBT-Gate-Ansteuerung | ||

Zum Einsatz mit Doppelimpuls-Prüfplatinen | ||

Kit-Klassifizierung Tochterplatine | ||

Vorgestelltes Gerät Enhanced isolated driver 1ED020I12-F2 | ||

Kit-Name EVAL-1ED020I12F2-DB | ||

Die zweite Revision der Infineon CoolSiC™-Evaluierungsplattform in einer Hoch-/Niederspannungsseite-Konfiguration mit zwei Gate-Treiber-ICs (1ED020I12-F2). Diese Plattform wurde entwickelt, um den optimalen Antrieb von CoolSiC™-MOSFETs oder anderen Leistungsschaltern wie IGBTs und MOSFETs in 3-poligen oder 4-poligen TO247-Gehäusen zu zeigen. Um dieses Ziel zu erreichen, wurde das Design in zwei Platinen aufgeteilt, eine Hauptplatine EVAL-PS-DP-MAIN und eine Tochterplatine, EVAL-1ED020I12F2-DB. Der modulare Ansatz ermöglicht eine zukünftige Erweiterung der Plattform mit zusätzlichen Gate-Treiberkarten. Der Schaltertyp kann frei gewählt werden. Unterstützt isolierte Gate-Treiber-Tochterplatine mit 1ED020I12-F2 zur Evaluierung von 1.200-V-CoolSiC™-MOSFETs. Der EVAL-1ED020I12F2-DB ist Teil der zweiten Revision der CoolSiC™-Evaluierungsplattform in einer Hoch-/Niederspannungsseite-Konfiguration mit zwei Gate-Treiber-ICs (1ED020I12-F2).

Einkanal-isolierter Gate-Treiber-IC (1ED-F2)

2 A, typischer Ausgangsstrom von Schiene zu Schiene

Präziser DESAT-Schutz, VCEsat-Erkennung

Aktive Miller-Klemme

Aktive Abschaltung und Kurzschlussklemme

28 V absolut max. Ausgangsspannung

170/165 ns typ. Ausbreitungsverzögerung

2 A, typischer Ausgangsstrom von Schiene zu Schiene

Präziser DESAT-Schutz, VCEsat-Erkennung

Aktive Miller-Klemme

Aktive Abschaltung und Kurzschlussklemme

28 V absolut max. Ausgangsspannung

170/165 ns typ. Ausbreitungsverzögerung

Diese Plattform wurde entwickelt, um den optimalen Antrieb von CoolSiC™-MOSFETs oder anderen Leistungsschaltern wie IGBTs und MOSFETs in 3-poligen oder 4-poligen TO247-Gehäusen zu zeigen. Um dieses Ziel zu erreichen, wurde das Design in zwei Platinen aufgeteilt: eine Hauptplatine EVAL-PS-DP-MAIN und eine