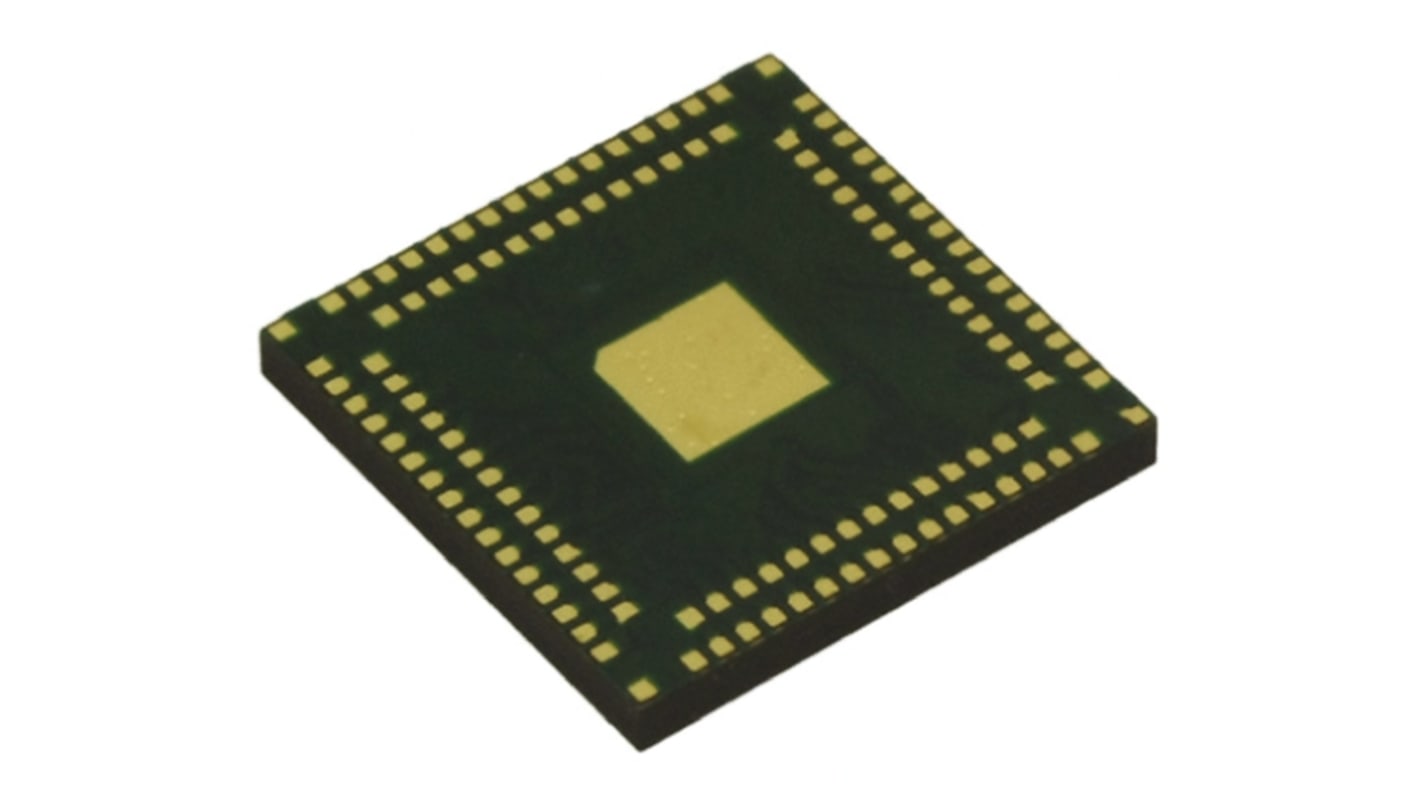

XMOS Mikrocontroller XS1 Multi-Core Oberfläche 128kB Flash QFN 124-Pin 60 MHz 128 kB RAM

- RS Best.-Nr.:

- 729-9951

- Herst. Teile-Nr.:

- XS1-L02A-QF124-C5

- Marke:

- XMOS

Abbildung stellvertretend für Produktreihe

Mengenrabatt verfügbar

Zwischensumme (1 Stück)*

CHF.33.906

Vorübergehend ausverkauft

- Versand ab 20. August 2026

Sie benötigen mehr? Benötigte Menge eingeben und auf „Lieferverfügbarkeit überprüfen“ klicken.

Stück | Pro Stück |

|---|---|

| 1 - 4 | CHF.33.91 |

| 5 - 9 | CHF.29.78 |

| 10 - 24 | CHF.28.99 |

| 25 + | CHF.28.28 |

*Richtpreis

- RS Best.-Nr.:

- 729-9951

- Herst. Teile-Nr.:

- XS1-L02A-QF124-C5

- Marke:

- XMOS

Technische Daten

Mehr Infos und technische Dokumente

Rechtliche Anforderungen

Produktdetails

Finden Sie ähnliche Produkte, indem Sie ein oder mehrere Eigenschaften auswählen.

Alle auswählen | Eigenschaft | Wert |

|---|---|---|

| Marke | XMOS | |

| Produkt Typ | Mikrocontroller | |

| Serie | XS1 | |

| Gehäusegröße | QFN | |

| Montageart | Oberfläche | |

| Pinanzahl | 124 | |

| Gerätekern | Multi-Core | |

| Schnittstellentyp | JTAG, SPI | |

| Programmspeicherkapazität | 128kB | |

| Taktfrequenz max. | 60MHz | |

| RAM Größe | 128kB | |

| Maximale Versorgungsspannung | 3.6V | |

| Maximale Verlustleistung Pd | 450W | |

| Anzahl der programmierbaren Ein/Ausgänge | 84 | |

| Betriebstemperatur min. | -40°C | |

| Maximale Betriebstemperatur | 85°C | |

| Normen/Zulassungen | REACH, RoHS3 | |

| Höhe | 1.11mm | |

| Länge | 10mm | |

| Minimale Versorgungsspannung | 3V | |

| Automobilstandard | Nein | |

| Programmspeicher-Typ | Flash | |

| Befehlssatz-Architektur | RISC | |

| Alle auswählen | ||

|---|---|---|

Marke XMOS | ||

Produkt Typ Mikrocontroller | ||

Serie XS1 | ||

Gehäusegröße QFN | ||

Montageart Oberfläche | ||

Pinanzahl 124 | ||

Gerätekern Multi-Core | ||

Schnittstellentyp JTAG, SPI | ||

Programmspeicherkapazität 128kB | ||

Taktfrequenz max. 60MHz | ||

RAM Größe 128kB | ||

Maximale Versorgungsspannung 3.6V | ||

Maximale Verlustleistung Pd 450W | ||

Anzahl der programmierbaren Ein/Ausgänge 84 | ||

Betriebstemperatur min. -40°C | ||

Maximale Betriebstemperatur 85°C | ||

Normen/Zulassungen REACH, RoHS3 | ||

Höhe 1.11mm | ||

Länge 10mm | ||

Minimale Versorgungsspannung 3V | ||

Automobilstandard Nein | ||

Programmspeicher-Typ Flash | ||

Befehlssatz-Architektur RISC | ||

- Ursprungsland:

- SG

XS1 Event-Driven Prozessor

Ein XS1 vereint mehrere XCore™-Prozessoren, jeder mit einem eigenen Speicher auf einem Chip. Die programmierbaren Prozessoren sind in dem Sinn universell, dass sie Sprachen wie z. B. C ausführen können; sie unterstützen auch direkt eine gleichzeitige Verarbeitung (Multithreading), Kommunikation und Ein- und Ausgabe. Ein Hochleistungsschalter unterstützt die Kommunikation zwischen den Prozessoren, und XMOS-Links zwischen den Chips sorgen dafür, dass Systeme leicht mit mehreren Chips aufgebaut werden können. Die XS1-Produkte sollen eine praktische Lösung bieten, mit Software viele Funktionen auszuführen, die normalerweise von Hardware erledigt werden; wichtige Beispiele dafür sind Schnittstellen und Ein- und Ausgabensteuerungen.

Jeder XCore-Prozessor bietet folgende Ressourcen:

32-Bit-Prozessor mit bis zu 500 MIPS

Acht Hardware-Threads und 32-Kanalenden

Zehn Zeitgeber und sechs Taktblöcke

Vier XMOS-Links

64 KB SRAM und 8 KB OTP-Speicher

Der XCore ist ein multithreaded Datenverarbeitungsbauteil mit Befehlssatzunterstützung für Kommunikation, Ein- und Ausgabe und Zeitsteuerung. Die Thread-Ausführung ist deterministisch, und die Dauer zur Ausführung einer Befehlsfolge kann genau vorausgesagt werden. Deshalb kann Software, die auf einem XCore läuft, viele Funktionen ausführen, die normalerweise von Hardware, insbesondere DSP und E/A, ausgeführt wird.

Jedes XCore-Thread hat einen dedizierten Registersatz, und die zeitliche Planung von Threads wird von der Hardware ausgeführt. Die Kommunikation zwischen Threads erfolgt über Hardwarekanäle. Kommunikationsbefehle übertragen Daten direkt zwischen Prozessorregistern und -kanälen, die automatisch den zeitlichen Ablauf der kommunizierenden Threads planen, um den Datenfluss zu steuern.

Der XCore hat einen effizienten Befehlssatz, um konventionelle sequenzielle Programmiersprachen zu unterstützen. Die Multithreading-, Kommunikations- und Ein- und Ausgabebefehle unterstützen moderne, nebenläufige Programmiersprachen. Der Befehlssatz ist leicht erweiterbar, um anwendungsspezifische Befehle aufzunehmen; dazu zählen derzeit Support für lange Arithmetik, CRC, DSP und Kryptografie.

Jeder XCore hat ein einzelnes, vereintes Speichersystem, das von allen vom Kern ausgeführten Threads für Programme und Daten gemeinsam benutzt wird. Mehrere Threads können das gleiche Programm im Speicher benutzen und die Datenhoheit übernehmen. Es werden keine Cachespeicher verwendet.

Der XCore hat einen dicht integrierten Satz an E/A-Anschlüssen, die direkt durch Befehle gesteuert werden. Daten werden direkt zwischen Prozessorregistern und Anschlüssen übertragen, um einen Speichereinsatz zu vermeiden und Latenzzeiten zu minimieren. Die Anschlüsse können nach Bedarf Daten seriell übertragen, damit der Prozessor Hochgeschwindigkeitsdatenströme handhaben kann. Sie können auch die Ankunft von Daten zeitlich markieren und genau die Zeitpunkte kontrollieren, zu denen die Daten an die oder von den Stiften übertragen werden.

Verwandte Links

- XMOS Mikrocontroller XS1 Multi-Core Oberfläche 128kB Flash QFN 124-Pin 60 MHz 128 kB RAM

- XMOS Mikrocontroller XS1-L01A-TQ128 Multi-Core Oberfläche Flash TQFP 128-Pin 60 MHz 64 kB RAM

- RS PRO, Multi-Core, Einzelader

- Wurth Elektronik, Einzelader, Multi-Core

- Jokari Abisolierer, Multi-Core 4 to 70 mm

- Ideal 45 Abisolierer, Multi-Core 26/16 AWG

- Jokari Abisolierer, Multi-Core 8 to 13 mm, 13 mm

- Jokari Abisolierer, Multi-Core 8 to 28 mm, 28 mm